Vitis HLS 学习笔记

1 第一个Vitis HLS工程

1 |

1 |

|

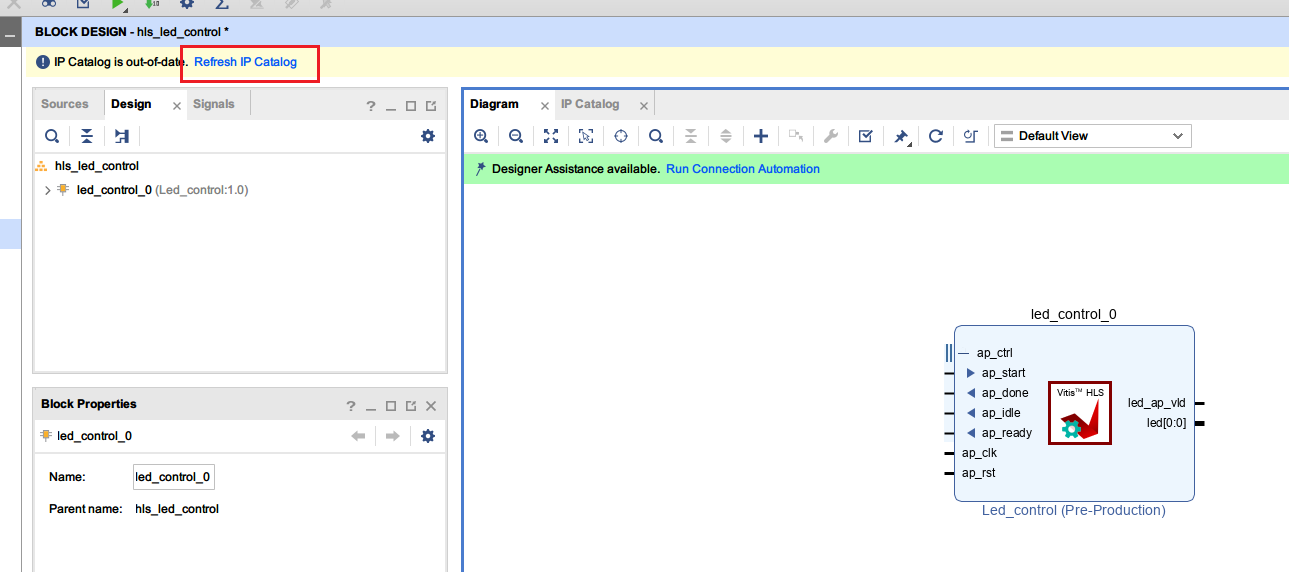

综合,导出RTL IP,创建一个Vivado工程,IP仓库选择Vitis HLS项目的存放路径,Vivado会自动识别到导出的IP。

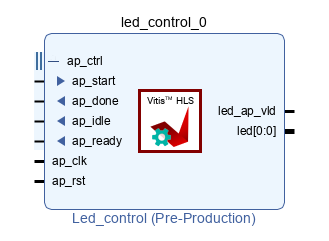

ap_start:检测到上升沿时IP里面的代码就开始运行;当ap_start和ap_done都为高电平时,程序中的代码就会循环执行;如果ap_start为低电平,则一次执行完成之后ap_done输出一个时钟周期的高电平后不再重复执行。ap_done:程序执行完毕之后,ap_done会输出一个时钟周期的高电平。ap_idle:指示IP的状态,如果是高电平说明此时IP没有执行代码。ap_ready:此时IP已经准备好接收新的数据。ap_clk:时钟ap_rst:复位,默认高电平复位,可以设置成低电平(暂时不知道怎么设置)led_ap_vld:输出数据有效

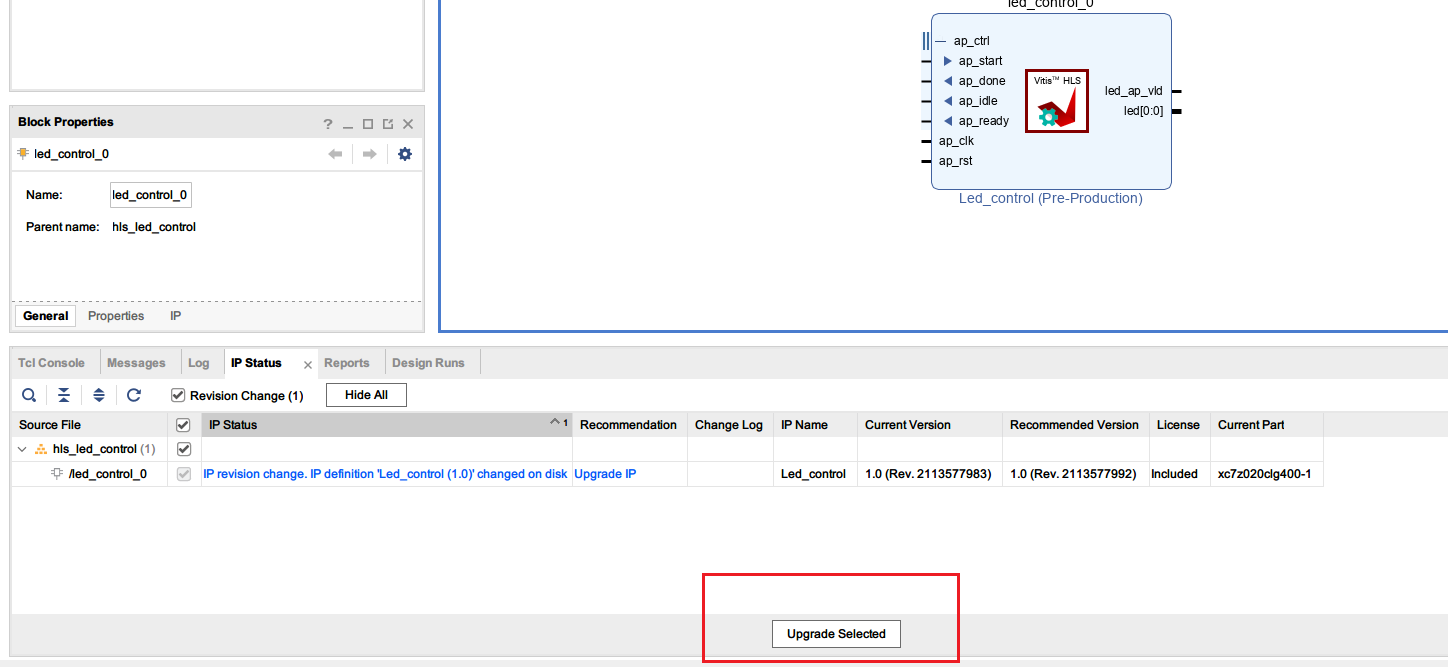

如果在Vitis中更新了文件,不需要在Vivado中重新添加路径。综合、RTL导出后直接在Vivado中选择刷新和升级即可。

之后的操作,写仿真文件,行为仿真,综合,布线,烧录和之前的开发流程没有区别。

2 Vitis HLS C/C++ 可综合规则

在Vitis HLS C/C++中,可综合的语句分为如下几种:

- 循环语句:Vitis HLS会对循环中的内容进行优化,例如流水线等

- 类定义:类可以被综合,但是其中的类方法不一定会被综合

- 函数:顶层函数会被综合成顶层模块。如果顶层模块中调用了其他函数,且它不是内联函数(函数定义可以直接替换),那会在顶层模块下方例化小型的模块。

- 数组

- 数据类型:包含标准数据类型,和任意精度的整形

ap_int<N>、ap_uint<N>(需要包含头文件ap_int.h)和任意精度的浮点型ap_fixed<N, M>(N是总位宽,M是整数部分位宽,需要包含头文件ap_fixed.h)。 - 结构体:会被拼接成一个独立的元素。如果不想拼接就需要分开写。

About this Post

This post is written by Yun Zhang, licensed under CC BY-NC 4.0.