FPGA数字图像处理课程

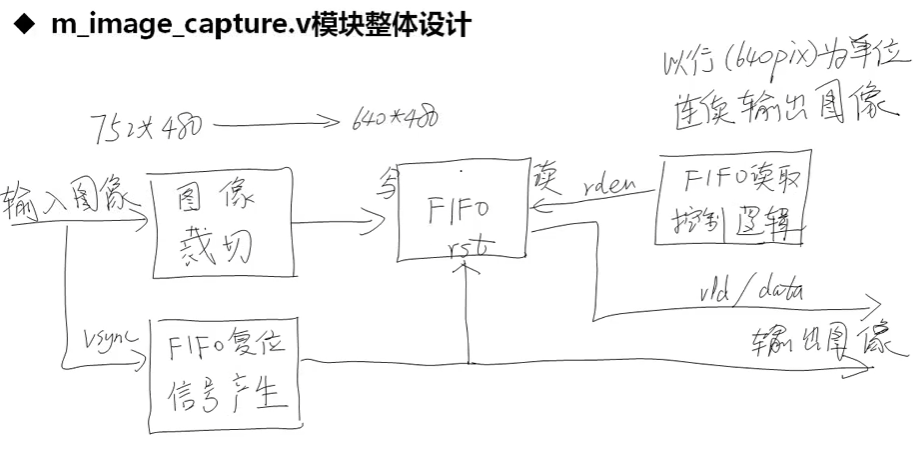

camera_capture模块中的FIFO处理,解决时钟域不同的问题。OV5640传入的数据速度是24MHz,而系统的时钟为50MHz。

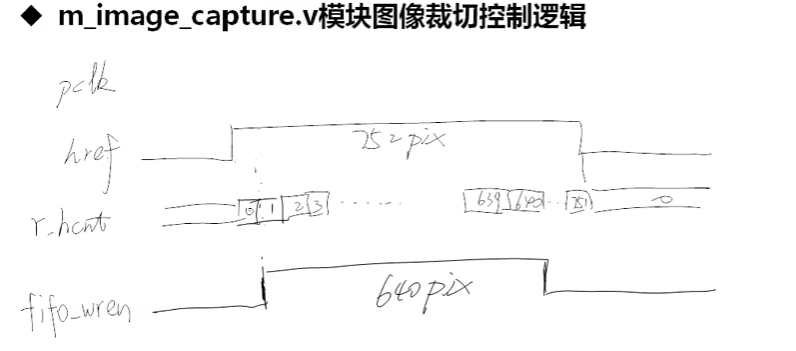

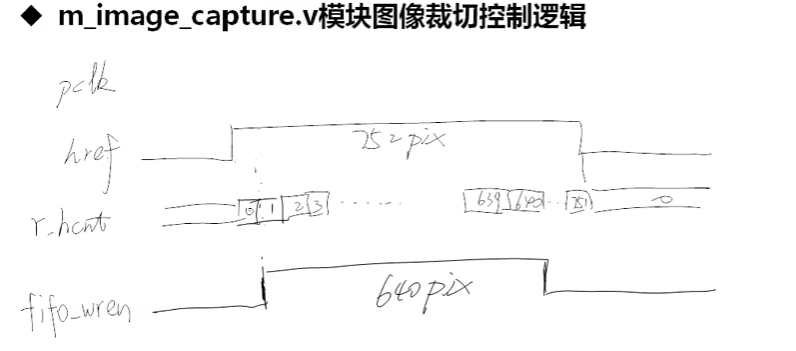

图像裁切控制逻辑(可能用不到)

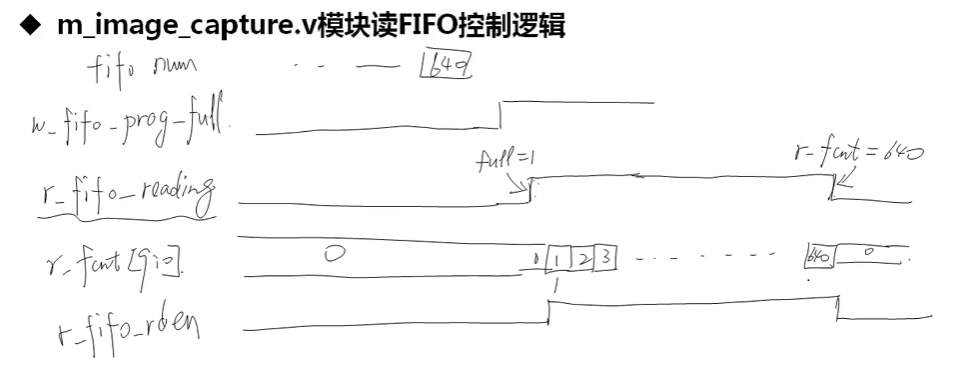

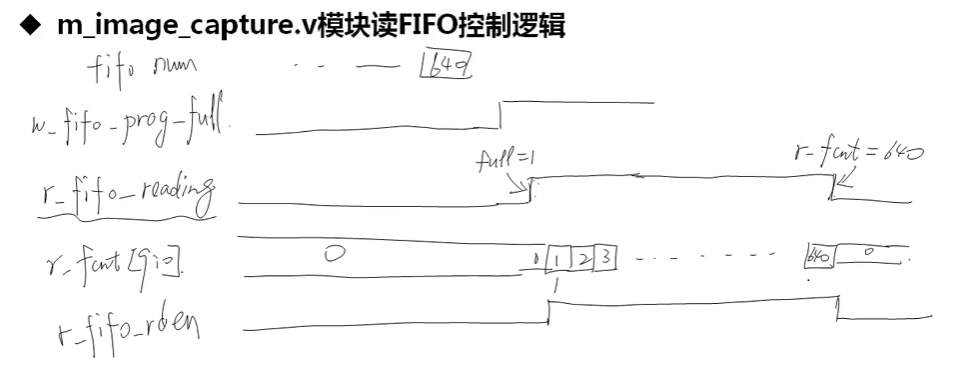

读FIFO控制逻辑

About this Post

This post is written by Yun Zhang, licensed under CC BY-NC 4.0.

camera_capture模块中的FIFO处理,解决时钟域不同的问题。OV5640传入的数据速度是24MHz,而系统的时钟为50MHz。

图像裁切控制逻辑(可能用不到)

读FIFO控制逻辑

This post is written by Yun Zhang, licensed under CC BY-NC 4.0.